- Produkte

-

Technologien

- IR LayerRelease™ Technology

- MLE™ - Maskless Exposure Technologie

- Nanopräge-Lithographie (NIL) - SmartNIL®

- Wafer-Level Optics

- Optische Lithographie

- Fotolackverarbeitung

- Temporäres Bonden und De-Bonden

- Eutektisches Bonden

- Transient Liquid Phase (TLP) Bonden

- Anodisches Bonden

- Metall-Diffusionsbonden

- Hybrid- und Fusionsbonden

- Die-to-Wafer Fusion and Hybrid Bonding

- ComBond® Technologie

- Metrologie

- Unternehmen

- Karriere

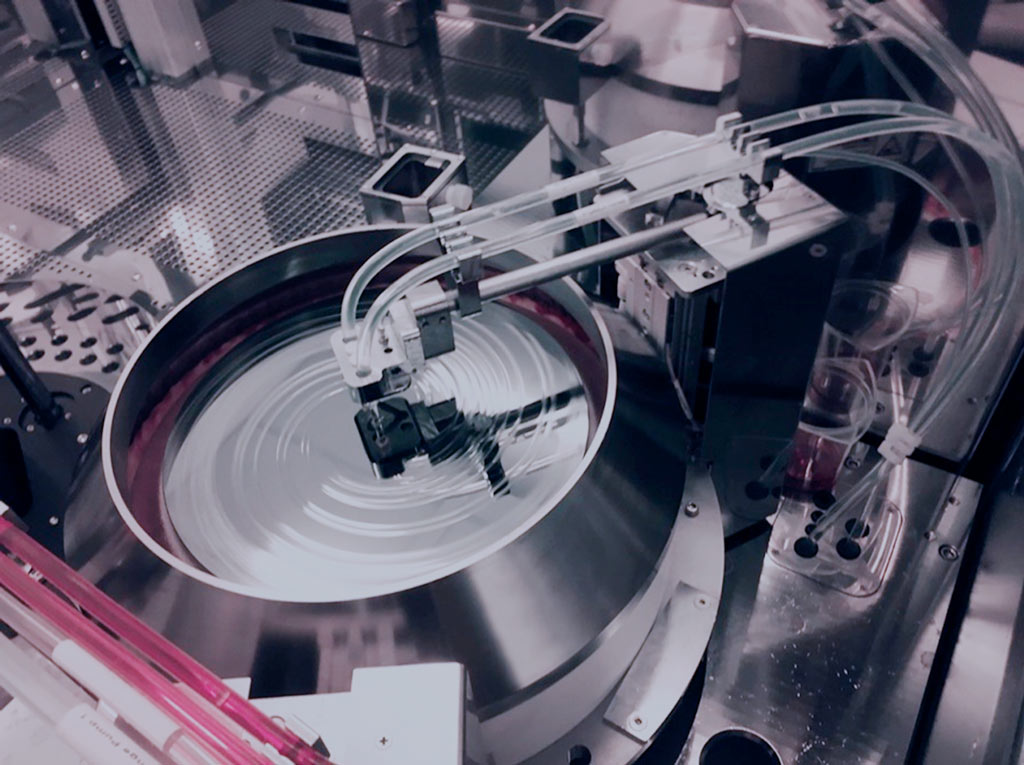

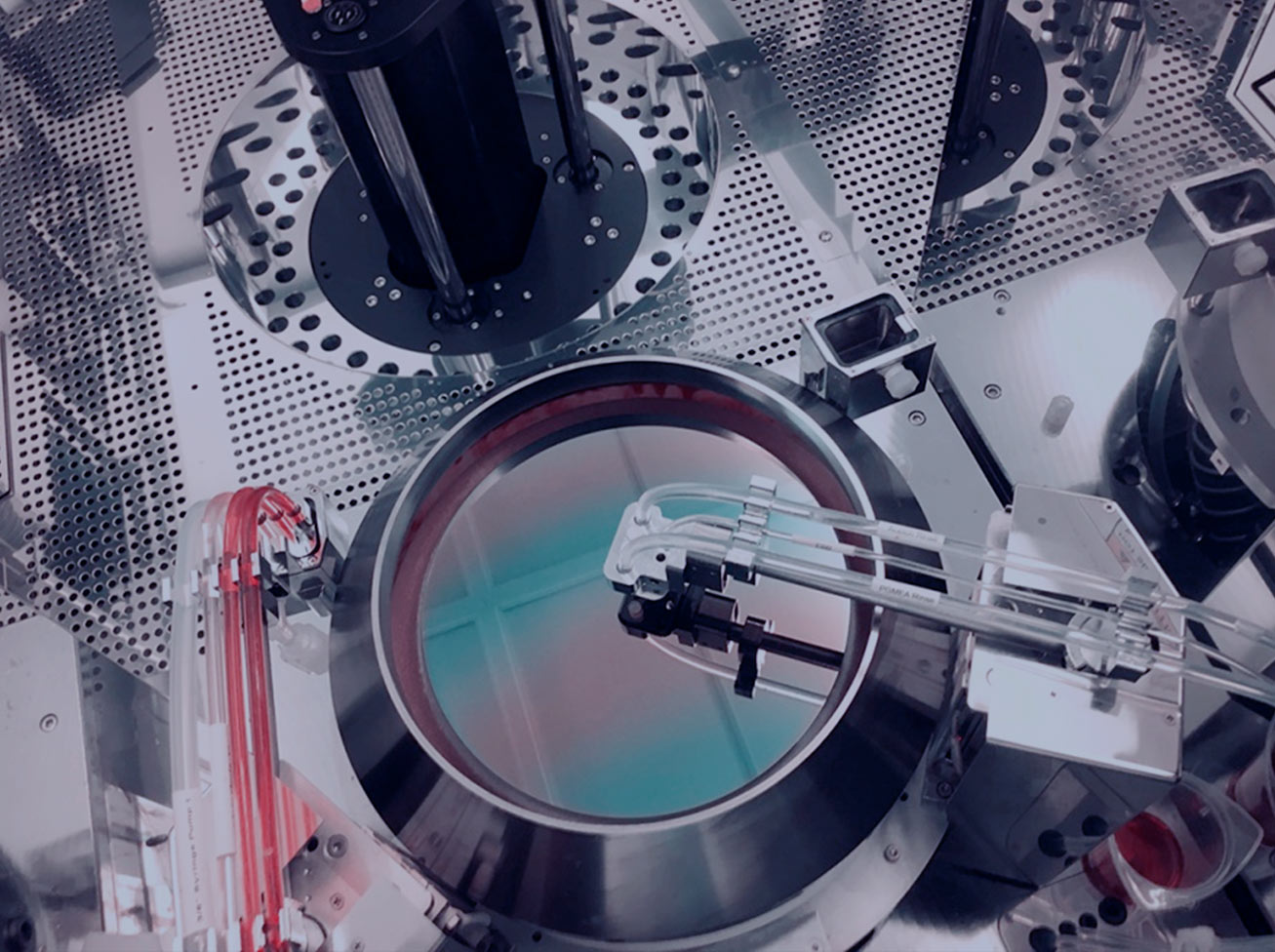

Spin Coating Technology

Spin coating still remains the preferred method of coating on planar surfaces.

Introduction

Spin coating technology is a universal and intensively used process for applying uniform thin films when no topography on the wafer is considered.

Related technologies

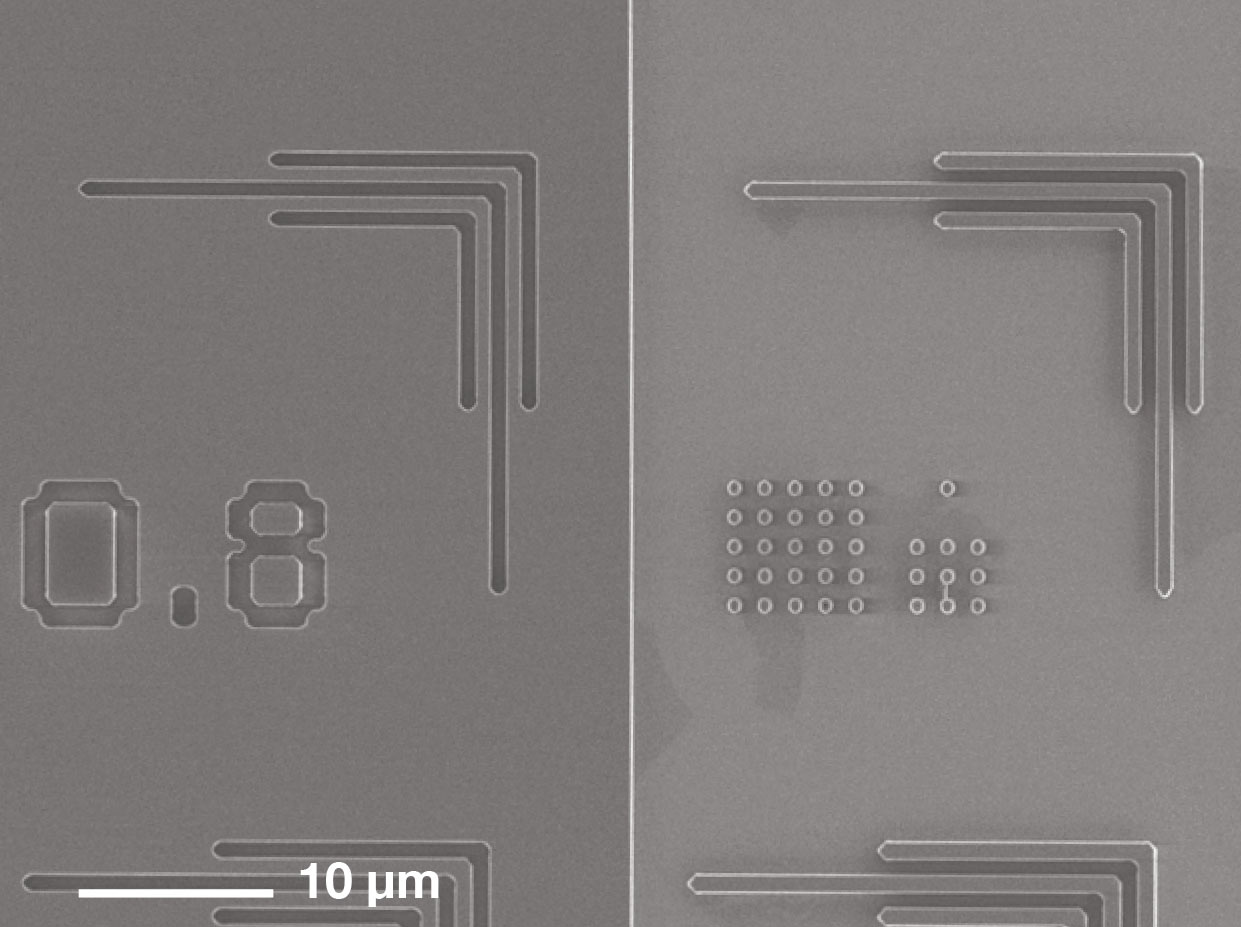

Dosing accuracy of dispensed material and spin speed are some of the most important factors in spin coating processes. Other critical process parameters such as acceleration, precise positioning or possibility to perform a dynamic dispense rate also play a significant role in coat properties. EVG spin coaters are designed to control all of these critical parameters to ensure precise resist dispensing process control. Up to eight dispense lines without temperature control or up to four temperature-controlled dispense lines enhance process set-up supporting three different dispense modes to guarantee optimum results for an extensive range of resists with viscosities up to 52.000 cP. Static or dynamic center dispense mode is recommended for typical thin-film applications and standard viscosity. Area dispense mode optimizes uniformity and resist consumption by enabling extremely uniform thick resist layers for the use of high-viscosity resists like BCB or SU-8. Moreover, edge dispense mode is a typical application for etch protection purposes, especially for long-term etch processes. For this purpose, EVG systems are equipped with programmable swivel arms supporting various flat/notch designs. Additional functions – such as solvent-based pre-wetting, edge-bead removal and automatically solvent refillable sealed park position – support advanced process control and production requirements. The programmable suck-back function prevents surplus resist from dropping out of the nozzle tip on the wafer surface and thus secures conformal results throughout the whole wafer. Optional CoverSpin reduces the amount of resist material per wafer and avoids edge turbulence effects independent of the substrate shape. Overall, EVG’s spin coat module with a simulation-based low-turbulence design effectively supports resist-saving processes while providing high-uniformity results on planar or low-topography surfaces.

Features

- Precise recipe-controlled resist dispensing process

- Three different dispense modes for extensive range of photoresists with viscosities up to 52000 cP

- Simulation-based low-turbulence design of coat module geometry

- Programmable swivel arm supporting various flat/notch designs

- Advanced process control with additional functions such as solvent-based pre-wetting or edge-bead removal

- Automatically solvent refillable sealed park position

- Programmable suck-back function

- CoverSpin™ technology for improved coating uniformity and eliminated edge effects independent of the substrate shape

- Smart process control and data analysis software features

- Integrated analysis features for process and machine control

- Parallel task/queueing task processing feature

- Equipment and process performance tracking feature

- Smart handling features

- Occurrences and alarms analysis

- Smart maintenance management and tracking

Talk to our EVG technology experts!

Questions?

Events

Semicon South East Asia 2026

Besuchen Sie unseren Stand #1126 und hören Sie sich unseren Vortrag “Advanced Lithography Technologies for Packaging: Enabling Next Gen Plasma Dicing Applications” auf der Techstage am 06. Mai gehalten von Deputy Process Technology Manager Europe Tobias Zenger an.

9th International Workshop on Low Temperature Bonding for 3D Integration LTB-3D 2026

Hören Sie sich unseren Vortrag über “Xenon vs Argon Ion Activation for Room‑Temperature Wafer Bonding of Si and SiC” an, gehalten von Senior Process Technology Engineer Peter Kerepesi.

Weitere Informationen finden Sie hier.

ITF World 2026

Besuchen Sie unseren Stand auf der IMEC ITF World 2026!

- IR LayerRelease™ Technology

- MLE™ - Maskless Exposure Technologie

- Nanopräge-Lithographie (NIL) - SmartNIL®

- Wafer-Level Optics

- Optische Lithographie

- Fotolackverarbeitung

- Temporäres Bonden und De-Bonden

- Eutektisches Bonden

- Transient Liquid Phase (TLP) Bonden

- Anodisches Bonden

- Metall-Diffusionsbonden

- Hybrid- und Fusionsbonden

- Die-to-Wafer Fusion and Hybrid Bonding

- ComBond® Technologie

- Metrologie

Questions about our technologies?

Contact the EVG experts