ダイ・トゥ・ウェーハ プラズマ活性化フュージョン/ハイブリッド接合

一括式または直接配置式ダイ・トゥ・ウェーハ接合

イントロダクション

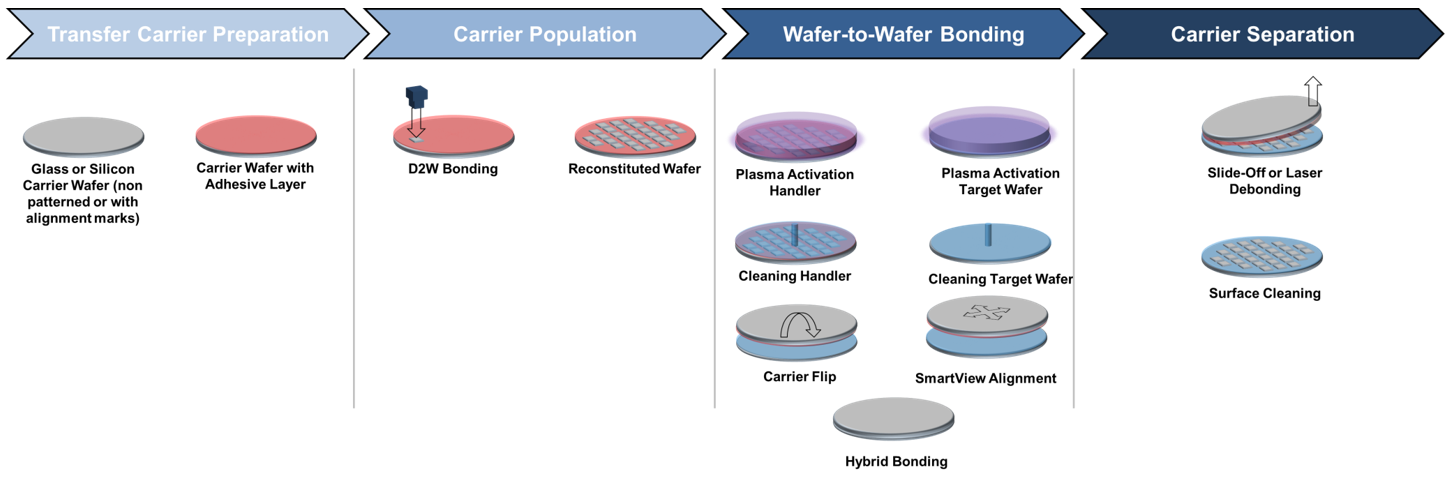

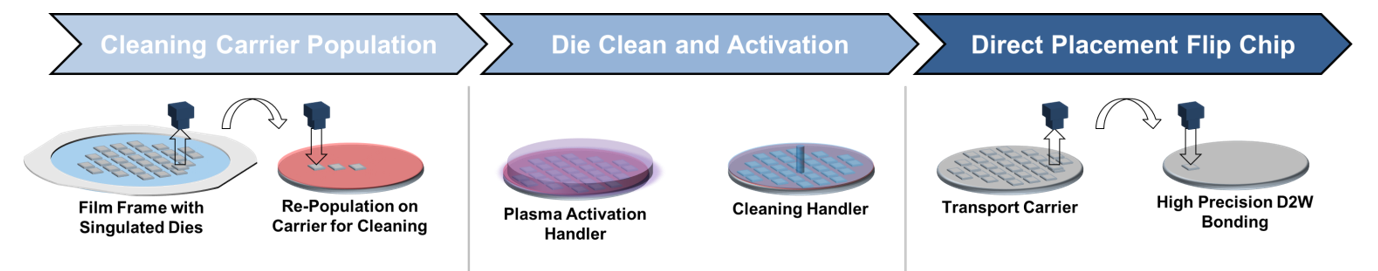

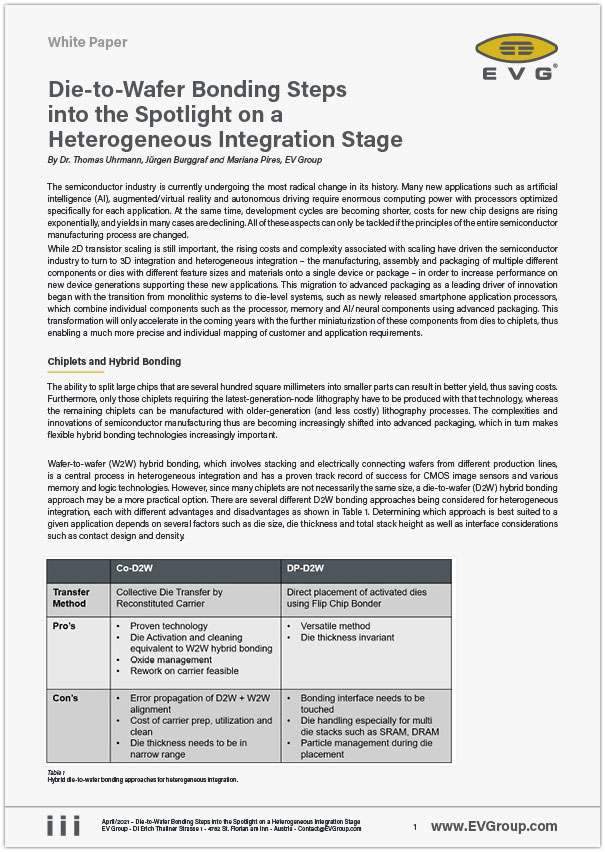

異なる生産ラインで製造されたウェーハを積層して電気的に接続するウェーハ・トゥ・ウェーハ(W2W)ハイブリッド接合は、ヘテロ集積化における中心的なプロセスであり、CMOSイメージセンサーや各種メモリとロジックの統合等、特定のアプリケーションで既に実証されています。しかし、多くのチップレットは必ずしも全てが同一サイズではないため、ダイ・トゥ・ウェーハ(D2W)によるハイブリッド接合が、ヘテロ集積化を可能にするための、より実用的な手段となります。ヘテロ集積化のためにいくつかの異なるD2W 接合方式が検討されています。それは、一括式D2W接合および直接配置式D2W接合で、以下の表に示すように、それぞれ長所と短所があります。

| Co-D2W(一括式) | DP-D2W(直接配置式) | |

|---|---|---|

| トランスファー方式 | 再構成キャリアによる一括式ダイ・トランスファー | フリップチップボンダーによる活性化済ダイの直接配置 |

| 長所 | - 確立された技術- W2W ハイブリッド接合と同等のダイ活性化と洗浄- 酸化膜の管理- リワーク可能な支持基板 | - 汎用的な手法- ダイ厚調整不要 |

| 短所 | - D2WとW2Wのアライメントエラーが加算- キャリアの準備、利用、洗浄にかかる費用- ダイ厚のばらつきを最小にする必要あり | - 接合界面への接触が必要- SRAM、DRAMなどのマルチダイスタック用途でのダイ搬送- ダイ配置時のパーティクル管理 |

EVG のヘテロジニアス・インテグレーション・コンピテンスセンター™ で技術開発を促進

これらの課題に対処するために、EVG はヘテロジニアス・インテグレーション・コンピテンス・センター(HICC) を設立しました。HICCは、お客様がEVGのプロセスソリューションおよびノウハウを活用することで、システム統合とパッケージング技術の進歩により可能となる新製品や機能強化品の開発およびアプリケーションの実現が出来るように支援します。お客様にとって開発のハードルをできるだけ低くし、EVGを新しいアイデアのインキュベーターとして提供することがHICC設立の基盤となっています。EVGは、HICCを通じて、ヘテロ集積化と先端パッケージングを用いて技術開発を加速し、最小限のリスクでお客様の技術および製品の差別化を図ることをお手伝いするとともに、商品化前の製品開発に必要とされる知的財産権の保護を最高水準で保証いたします。

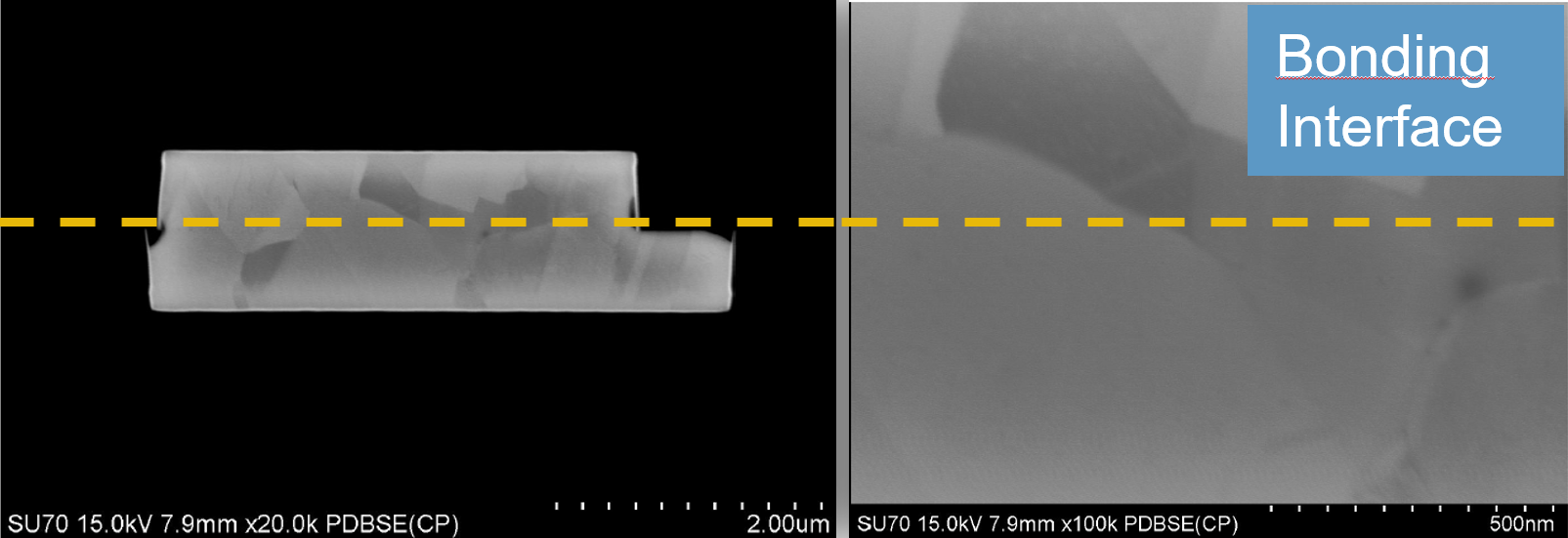

一括式D2W接合(Co-D2W)を用いてハイブリッド接合したダイのTEM断面画像

Talk to our EVG technology experts!

Questions?

Events

ITF World 2026

Visit our booth at ITF World 2026!

ECTC 2026

Visit our booth #220 and visit our PDC "Wafer-to-Wafer and Die-to-Wafer Hybrid Bonding for Heterogeneous Integration and Advanced Packaging" on Tue, May, 26 and listen as well to our talk “Digital Lithography Patterning of Novel Dry Film Resists for High Aspect Ratio Cu Pillar Applications on 310x310mm2 Panel Substrates” held by Business Development Manager Dr. Ksenija Varga on 29th of May.

Here you'll find more information on the program.

Questions about our technologies?

Contact the EVG experts