- Products

-

Technologies

- IR LayerRelease™ Technology

- MLE™ - Maskless Exposure Technology

- Nanoimprint Lithography (NIL) - SmartNIL®

- Wafer Level Optics

- Optical Lithography

- Resist Processing Technology

- Temporary Bonding and Debonding

- Eutectic Bonding

- Transient Liquid Phase (TLP) Bonding

- Anodic Bonding

- Metal Diffusion Bonding

- Hybrid and Fusion Bonding

- Die-to-Wafer Fusion and Hybrid Bonding

- ComBond® Technology

- Metrology

- Company

- Careers

Metrology

Process control and optimization for lithography and bonding

Introduction

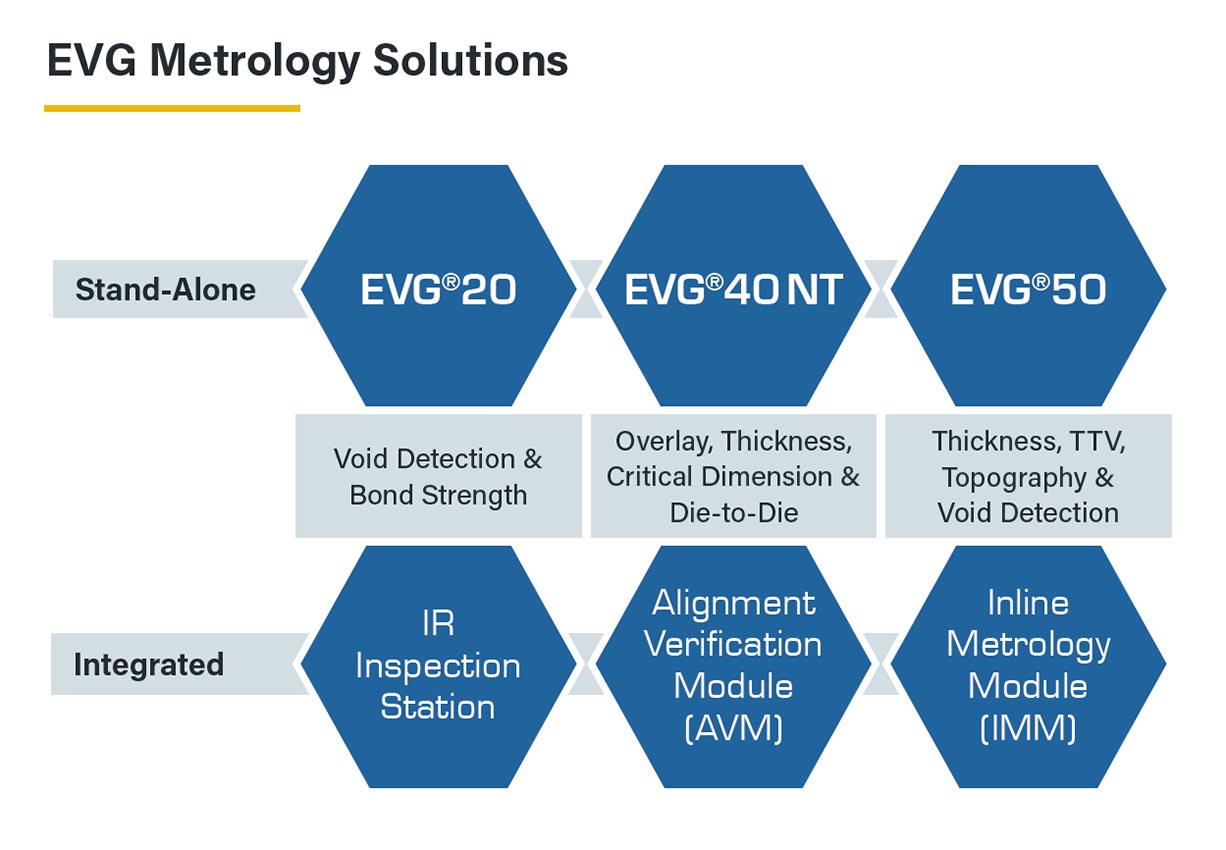

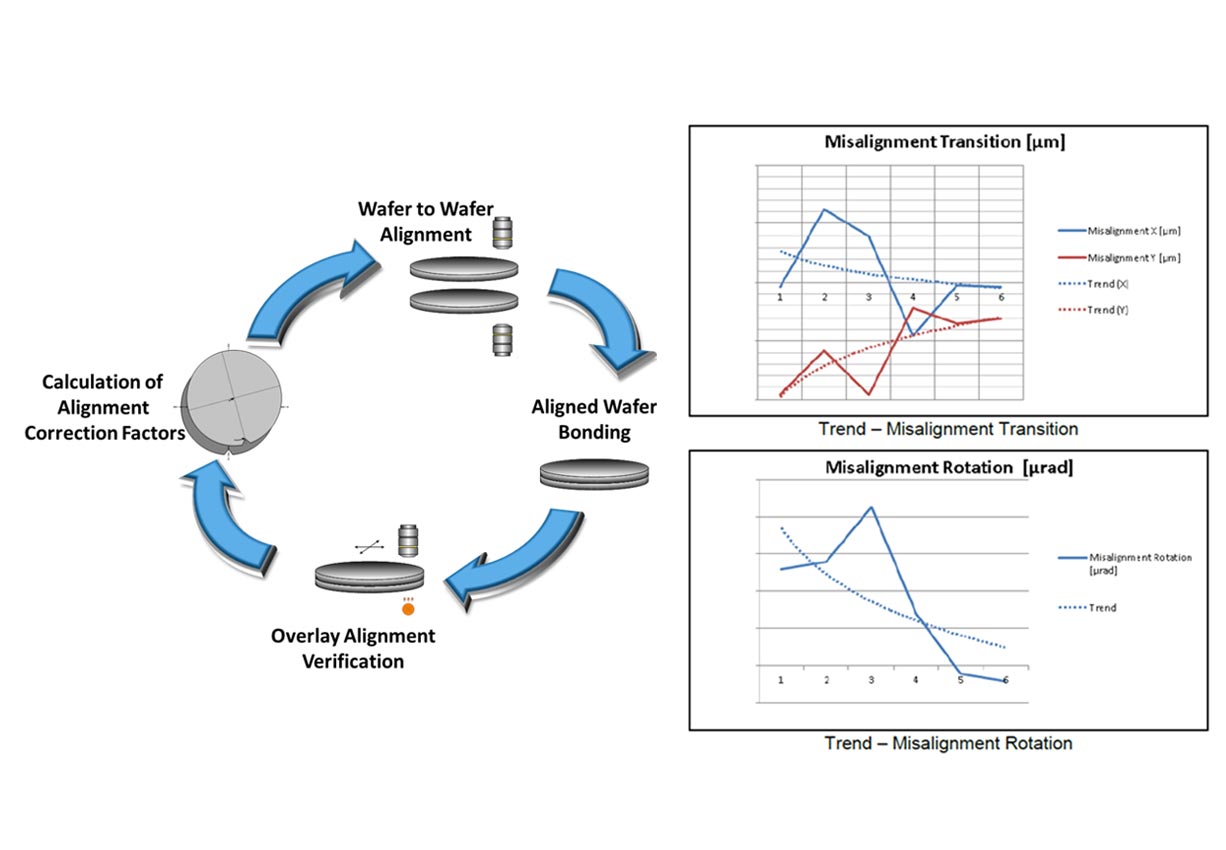

To complete EVG’s lithography and bonding portfolio, sufficient metrology is necessary to ensure process control and (in combination with feedback loops) also allow for process parameter optimization like bond alignment. Versatile measurement options are available to meet the metrology requirements for a wide variety of applications. These tools can fit in HVM and R&D environments.

Metrology is essential to control, optimize and ensure the highest yield in semiconductor manufacturing processes. Advanced packaging, MEMS and photonic applications are gaining importance, very often lacking suitable metrology solutions for essential processing steps. Furthermore, overall performance of the device is determined by packaging and back-end-of-line processes; hence, process requirements are getting tighter and need further metrology. EVG’s metrology solutions for wafer inspection and evaluation are optimized for lithography and all types of bonding applications. As one example, metrology prior to non-reworkable processes like wafer thinning after temporary bonding directly leads to increased yield and process security, where an integrated feedback loop results in a reduction of high-cost wafer scrap.

Features

- Adaptiveness

- Multi-sensor measurement mount for highest metrology flexibility

- Sensor set available for multiple measurement ranges and materials

- Self-calibration of measurement units for minimum service and maintenance

- Integration in stand-alone or production tool

- Handling

- Handling and metrology of various substrates materials, shapes, stress, bow or warp

- Bridge capability for different substrate sizes and carrier mounted wafers

- Available with multiple load port options and combinations

- Control

- Feedback loop for correction of process parameters

- Customized Pass/Fail criteria for automated processing decisions

- Fully integrated SECS/GEM interface

Related products

Talk to our EVG technology experts!

Questions?

- IR LayerRelease™ Technology

- MLE™ - Maskless Exposure Technology

- Nanoimprint Lithography (NIL) - SmartNIL®

- Wafer Level Optics

- Optical Lithography

- Resist Processing Technology

- Temporary Bonding and Debonding

- Eutectic Bonding

- Transient Liquid Phase (TLP) Bonding

- Anodic Bonding

- Metal Diffusion Bonding

- Hybrid and Fusion Bonding

- Die-to-Wafer Fusion and Hybrid Bonding

- ComBond® Technology

- Metrology

Questions about our technologies?

Contact the EVG experts