现在,异构集成受到越来越多的关注,业界认为异构集成能够提高计算性能,增加器件的功能,同时可避免连续缩放尺寸。自适应图案化技术可以解决小芯片设计持续创新以及将其集成在硅或封装上的需求。要实现这种新的行业愿景,就需要使用能快速集成新设计方案的全新大批量生产工具,因为传统后端光刻技术存在一些适用性限制。此外,各种布局设计和掩模库存管理成本的不断增加,也对总体开发和生产成本带来了很大影响。EV Group 开发的 MLE 技术解决了设计灵活性这一关键需求,它能应对开发和生产阶段的掩模相关难题,从而缩短开发周期。此外,使用该技术时,由于无需发送到外部,您的特定设计和布局都能得到保密,无泄露风险。这项创新型“数字光刻”技术不仅填补了研发与生产之间的鸿沟,也提供了一种可扩展解决方案,它能够同步动态处理芯片和晶圆级设计,同时还能满足先进封装、MEMS、生物医学和 HDI PCB 等市场的重要需求。

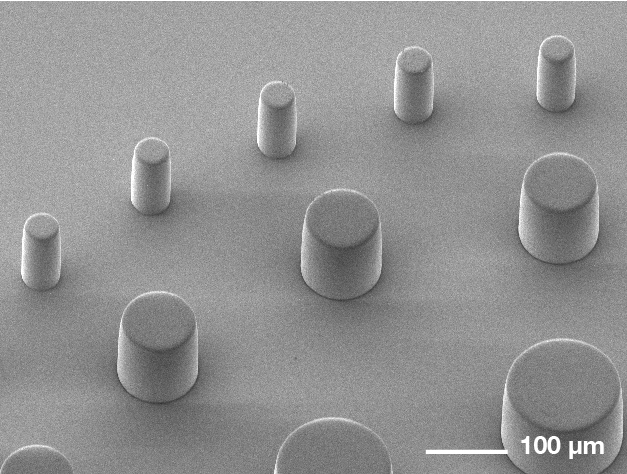

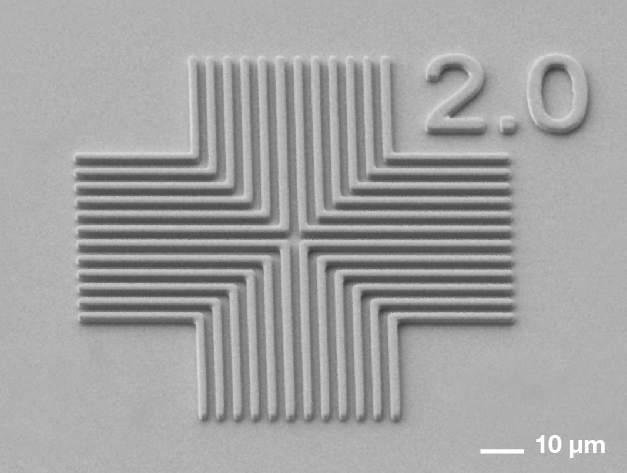

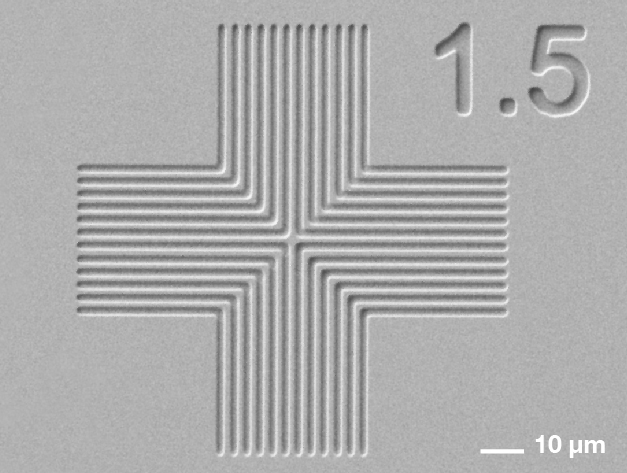

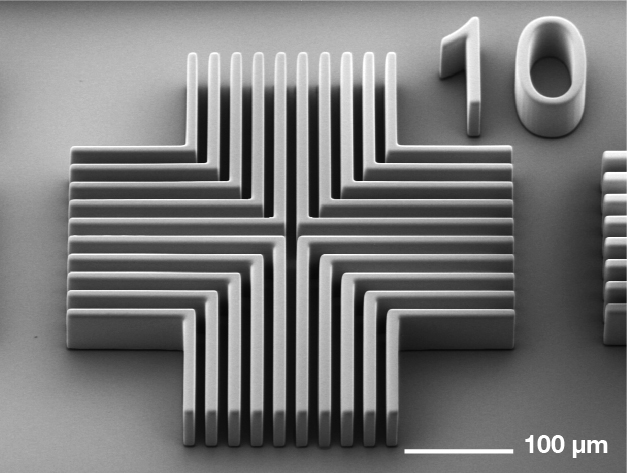

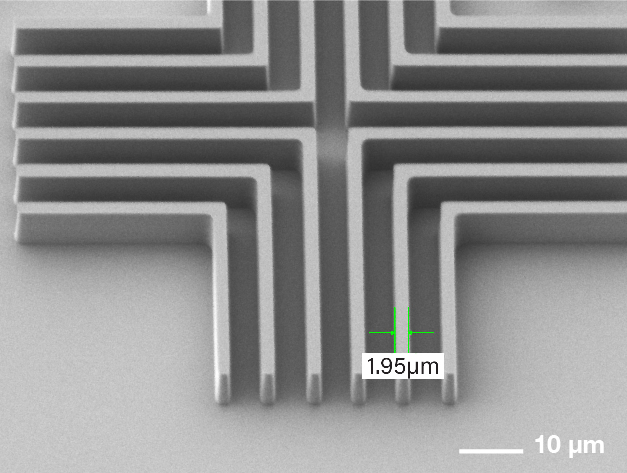

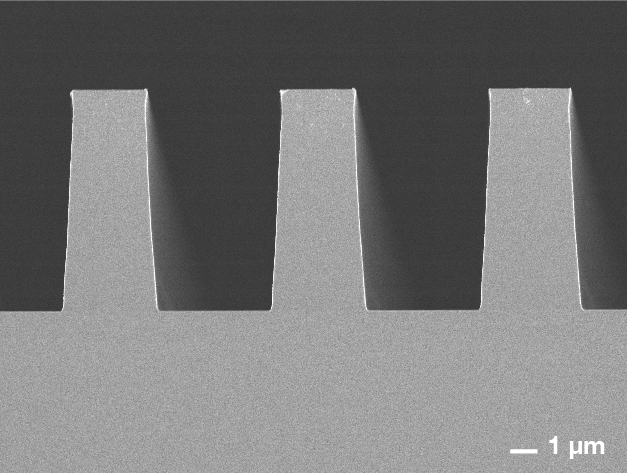

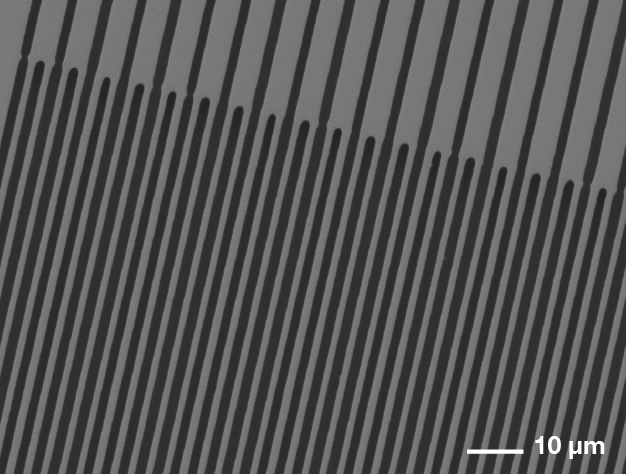

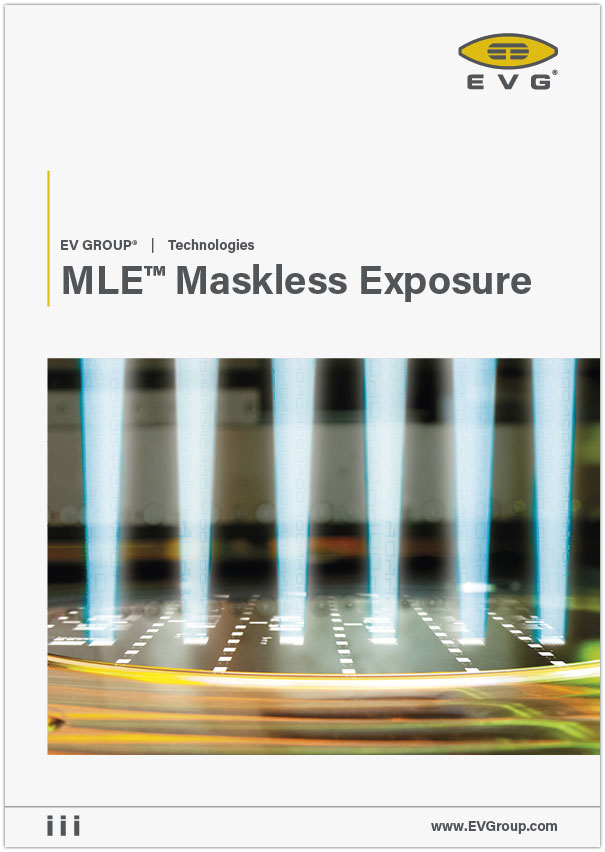

EVG 的 MLE 技术能够使整个基板表面实现高分辨率(线宽/线间距分辨率小于 2 µm)无线迹无掩模曝光,并且产量高,拥有成本低。该系统可通过添加或移除 UV 曝光头来根据用户需求进行扩缩,有助于加快从研发转到大批量生产的过程,提高产量,或根据基板尺寸和材料进行调整,因此非常适用于处理从小型硅或化合物半导体晶圆到面板大小的各种基板。利用灵活且可扩展的高功率 UV 激光器(具有多种曝光波长选择),无论是哪种光刻胶,MLE 都能提供同等的图案化效果。

EVG 开发创新 MLE 技术的目的,不仅是要将新型光刻工具推向市场,而且还要满足半导体行业对智能和敏捷数字处理的关键需求,同时也旨在针对产量、格式和无耗材基础设施提供独特的无掩模可扩展性。

特性

- 全分辨率、无线迹、动态光刻图案化

- 任意方向的线宽/线间距分辨率均小于 2 µm

- 布局数字编程,实现了设计自由和数据保密

- 单独芯片注释(序列号、加密密钥等)

- 晶圆级自适应配准补偿

- 不受基板变形和翘曲(厚晶圆、玻璃或有机基板)影响

- 智能、敏捷的数字光刻处理基础设施

- 无耗材技术

图片

Related products

Talk to our EVG technology experts!

Questions?

Events

Semicon South East Asia 2026

Visit our booth #1126 and listen to our talk “Advanced Lithography Technologies for Packaging: Enabling Next Gen Plasma Dicing Applications” at the Techstage on 06th of May held by Deputy Process Technology Manager Europe Tobias Zenger.

9th International Workshop on Low Temperature Bonding for 3D Integration LTB-3D 2026

Listen to our talk “Xenon vs Argon Ion Activation for Room‑Temperature Wafer Bonding of Si and SiC” held by Senior Process Technology Engineer Peter Kerepesi.

More information here.

ITF World 2026

Visit our booth at ITF World 2026!

Share this page with your colleagues on LinkedIn

Questions about our technologies?

Contact the EVG experts