- Products

- Technologies

- IR LayerRelease™ Technology

- MLE™ - Maskless Exposure Technology

- Nanoimprint Lithography (NIL) - SmartNIL®

- Wafer Level Optics

- Optical Lithography

- Resist Processing Technology

- Temporary Bonding and Debonding

- Eutectic Bonding

- Transient Liquid Phase (TLP) Bonding

- Anodic Bonding

- Metal Diffusion Bonding

- Fusion and Hybrid Bonding

- Die-to-Wafer Fusion and Hybrid Bonding

- ComBond® Technology

- Metrology

- Company

- Careers

Temporary Bonding and Debonding

Temporary bonding and debonding enabling backside processing for 3D integration

Introduction

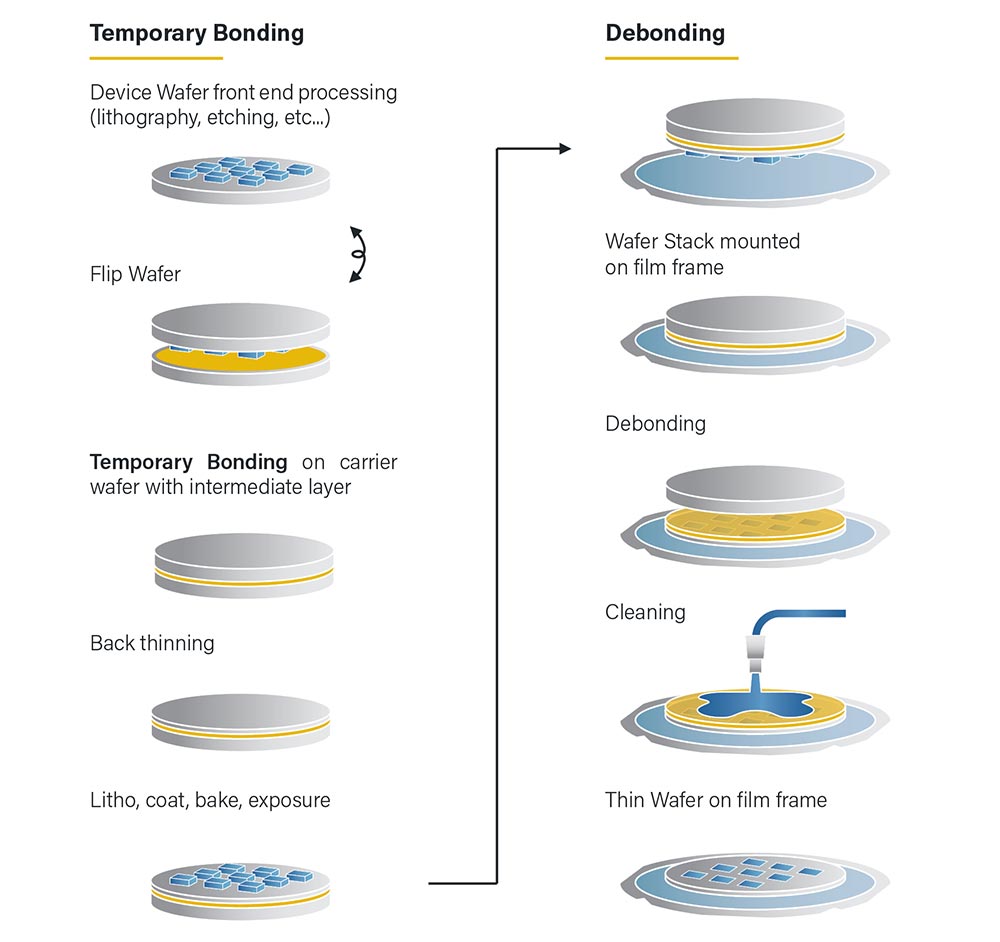

Temporary bonding is an essential process to offer mechanical support for thin or to-be-thinned wafers, which are key for 3D IC, power device and FoWLP wafers, as well as for handling fragile substrates like compound semiconductors. EVG’s outstanding bonding know-how includes temporary bonding equipment, which has been provided by the company since 2001.

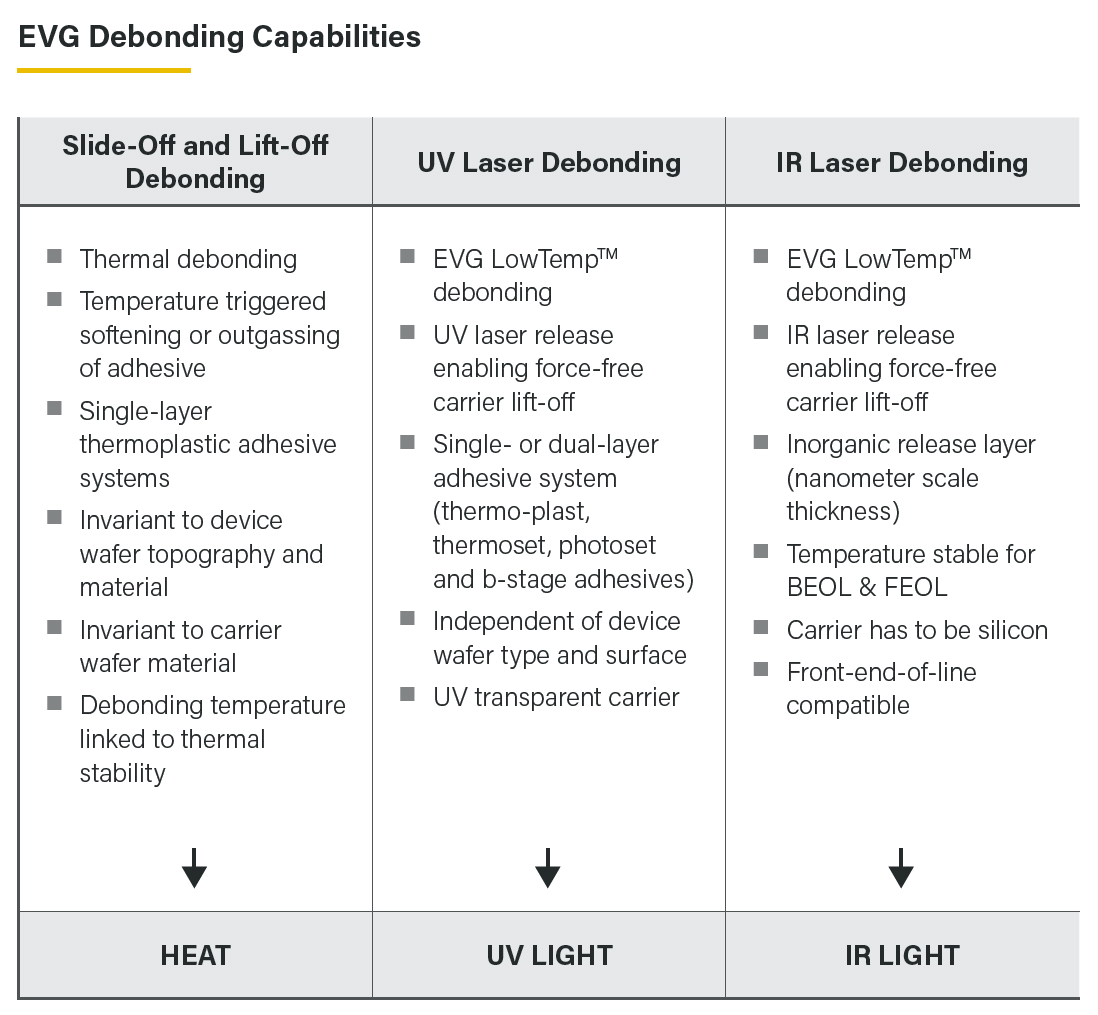

EVG’s open adhesive platform supports all commercially available materials, offering full process integration for temporary bonding and debonding. Adhesives are mainly classified by their debonding mechanism (weakening the adhesive bond between the device and carrier wafer), which is based on laser, mechanical force or temperature. Slide-off and lift-off debonding mark the starting point of temporary bonding at EVG with more than 20 years of experience. More recent developments of mechanical and UV-laser-initiated debonding are combined in EVG’s LowTemp debonding process, where the debond temperature is around room temperature. Especially for recent developments in advanced packaging, LowTemp debonding technologies are essential steps to enable back-side processing of silicon as well as the production of ultra-thin chips and packages for next-generation devices.

Features

- Open adhesive platform

- Modular tool layout – throughput optimized depending on specific process

- Bridge capability for different substrate sizes

- Available with multiple load port options and combinations

- Integrated metrology enables feedback loop for high-yield processes in automated tools

- Software monitoring of the whole process

- Fully integrated SECS/GEM interface in automated tool

Figures

Talk to our EVG technology experts!

Questions?

Related products

- IR LayerRelease™ Technology

- MLE™ - Maskless Exposure Technology

- Nanoimprint Lithography (NIL) - SmartNIL®

- Wafer Level Optics

- Optical Lithography

- Resist Processing Technology

- Temporary Bonding and Debonding

- Eutectic Bonding

- Transient Liquid Phase (TLP) Bonding

- Anodic Bonding

- Metal Diffusion Bonding

- Fusion and Hybrid Bonding

- Die-to-Wafer Fusion and Hybrid Bonding

- ComBond® Technology

- Metrology

Questions about our technologies?

Contact the EVG experts